تحقیق تأخیر CNTFET با CNT های غیررسوبی توسط تنظیم عرض دروازه ورودی

دانلود تحقیق تأخیر CNTFET با CNT های غیررسوبی توسط تنظیم عرض دروازه ورودی

در قالب Word و در ۴۲ صفحه، قابل ویرایش، شامل:

چکیده

مقدمه

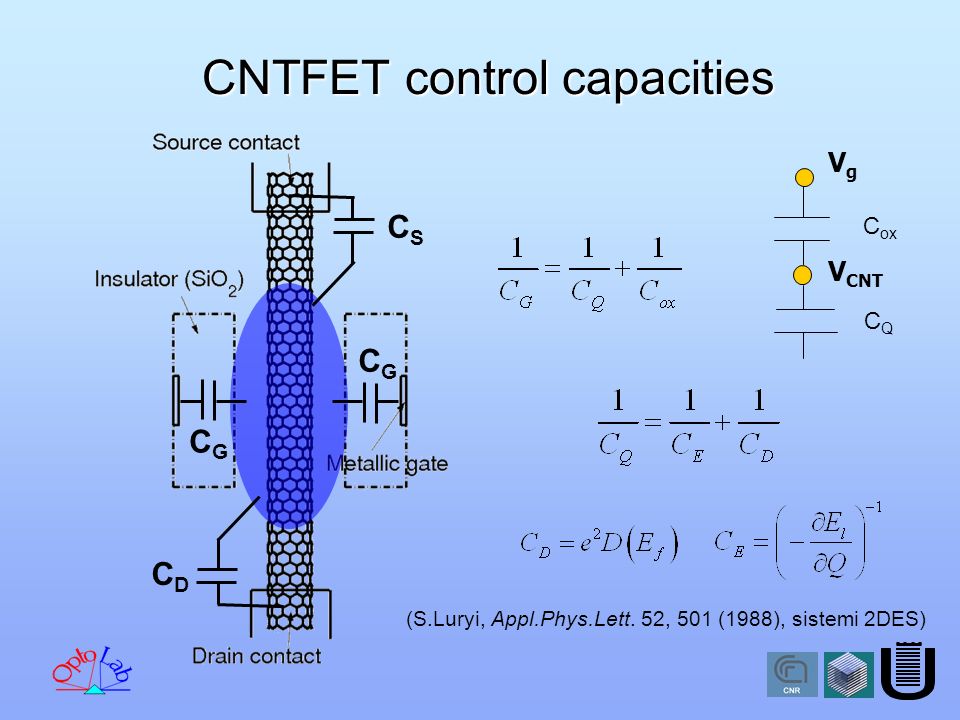

۲- مروری بر CNTFET

۳- تجزیه و تحلیل تأخیر توسط NCD و PCD

شکل ۱- ساختار CNTFET

شکل ۲- مراحل تولید CNTFET

الگوریتم ۱: تأخیر در یک CNTFET با CNTهای غیر رسوبی [۳]

شکل ۴- تأخیر در مقایسه با [NCDVGS=0.9 V,19,0,N=9,Vg=32nm[3

۴- تجزیه و تحلیل احتمالاتی تأخیر

شکل ۶- مجموع دو فاصلهی بین CNTها (int1+int2) برای بیشترین تأخیر در مقابل [NCDVGS=0.9 V,19,0,N=9[3

شکل ۷- مجموع دو فاصلهی بین CNTها (int1+int2) برای حداقل تأخیر در مقابل [NCDVGS=0.9 V,19,0,N=9[3

شکل ۹- PROBPCD، افزایش تأخیر و RSD در مقابل

جدول ۱: احتمال PCD برای بزرگترین و کوچکترین تأخیر [VGS=0.9 V,19,0,N=9) [3)

۵- تأخیر و کایرالیتی

شکل ۱۰- تأخیر (a ارزش متوسط و b (بزرگترین) (کوچکترین) ارزشها در مقابل ارزشهای میانه برای احتمال PCD در انحرافهای استاندارد متفاوت تحت توزیع نرمال (VGS=0.9 V,19,0,N=9,Wg=32nm)

۶- تنظیم پهنای گیت

شکل ۱۱- تأخیر در کایرالیتی متفاوت در مقابل NCD)VGS=0.9 V,19,0,N=9,Wg=32nm)

شکل ۱۲- ارزشهای متوسط تأخیر در مقابل ارزشهای میانه برای PCD در ارزشهای متنوع انحراف استاندارد و کایرالیتی (VGS=0.9 V,19,0,N=9,Wg=32nm)

شکل ۱۳- بزرگترین و کوچکترین تأخیر در مقابل ارزشهای میانه برای احتمال PCD با انحراف استاندارد متنوع و کایرالیتی (VGS=0.9 V,19,0,N=9,Wg=32nm)

شکل ۱۴- کاهش Wg)Wrg=1 CNT ,Wrg=2 CNTs)

شکل ۱۵- روش پیشنهاد شده برای تنظیم Wg

شکل ۱۶- تأخیر در مقایسه با NCD با تنظیم Wg برای کاهش تأخیر (الگوریتم ۲) (VGS=0.9 V,19,0,N=9,Wg=32nm)

شکل ۱۷- تأخیر در مقایسه با NCD با تنظیم Wg برای کاهش انحراف (الگوریتم ۳) (VGS=0.9 V,19,0,N=9,Wg=32nm)

شکل ۱۸- تأخیر و انحراف در مقایسه با NCD، زمانی که Wg برای کاهش تأخیر تنظیم شده باشد (الگوریتم ۲) در کایرالیتیهای متفاوت (VGS=0.9 V,19,0,N=9,Wg=32nm)

شکل ۱۹- تأخیر در مقایسه با NCD زمانی که Wg تنظیم شده برای کاهش انحراف باشد (الگوریتم ۳) در ارزشهای متفاوت کایرالیتی (VGS=0.9 V,19,0,N=9,Wg=32nm)

۷- تنظیم برای انحراف تأخیر کاهش یافته

الگوریتم ۲- الگوریتمی برای تنظیم Wg

شکل ۲۰- کاهش در تأخیر متوسط به درصد و انحراف متوسط بین تأخیر متوسط و حداقل تأخیر به درصد در مقابل کایرالیتی، زمانی که Wg برای کاهش تأخیر تنظیم شده است (الگوریتم ۲) و انحراف (الگوریتم ۳) (VGS=0.9 V,N=9,Wg=32nm)

شکل ۲۱- کاهش در تأخیر متوسط به درصد در مقایسه با کایرالیتی در زمان تنظیم Wg برای کاهش تأخیر (الگوریتم ۲) و انحراف (الگوریتم ۳) در مقادیر انحراف استاندارد از ۰۱/۰ و ۱/۰ (VGS=0.9 V,N=9,Wg=32nm)

شکل ۲۲- کاهش در انحراف متوسط به درصد در مقایسه با کایرالیتی با Wg تنظیم شده برای کاهش تأخیر (الگوریتم ۲) و انحراف (الگوریتم ۳) در مقادیر در مقادیر انحراف استاندارد از ۰۱/۰ و ۱/۰ (VGS=0.9 V,N=9,Wg=32nm)

جدول ۲- خلاصهای از نتایج پیشنهاد شده توسط تنظیم Wg

۸- نتیجهگیری

جهت دانلود رایگان نسخه انگلیسی این مقاله، اینجا کلیک نمایید.

چکیده

این مقاله مربوط به عملکرد لولههای نانوکربنی ترانزیستور اثر فیلد (CNTFET) در حضور CNTهای غیر رسوبی به عنوان نقص میباشد. یک تجزیه و تحلیل مبتنی بر شبیهسازی تنزل تأخیر به دلیل ویژگیهای مختلف (مانند کایرالیتی و توزیع CNT معیوب) از ابتدا دنبال شده است. دو راه حل برای کاهش تغییر در تأخیر ارائه شده است. این روش ها بر تنظیم عرض دروازه CNTFET توسط لیتوگرافی (و از بین بردن CNTها) به عنوان بخشی از فرآیند ساخت استوار شده است. این دو روش، تأخیر متوسط و انحراف آن را به ترتیب، کاهش میدهد. سپس، تجزیه و تحلیل تأخیر در قالب احتمالات ارائه شد.

عملکرد دو روش تنظیم پیشنهادی توسط ویژگیهای CNT (مانند کایرالیتی و توزیع نقص)، شبیهسازی و روشهای مبتنی بر احتمالات، مورد بررسی قرار گرفته است. توسط شبیهسازی قطعی (احتمالاتی)، اولین روش، به طور متوسط تأخیر را در حدود ۶٫۹۶۸% (۷٫۸۱۱%) کاهش میدهد؛ در حالی که انحراف، در حدود ۳۲٫۴۴۴% (۹٫۷۸۸%) افزایش (کاهش) مییابد. روش دوم، قطعی (احتمالاتی) به طور متوسط، انحراف را در حدود ۴۴٫۱۵۹% (۴۷٫۴۷۶%) با ۲٫۱۶۶% (۴٫۴۰۹%) کاهش تأخیر، میکاهد.

دیدگاهها (0)

نقد و بررسیها

هنوز بررسیای ثبت نشده است.